-

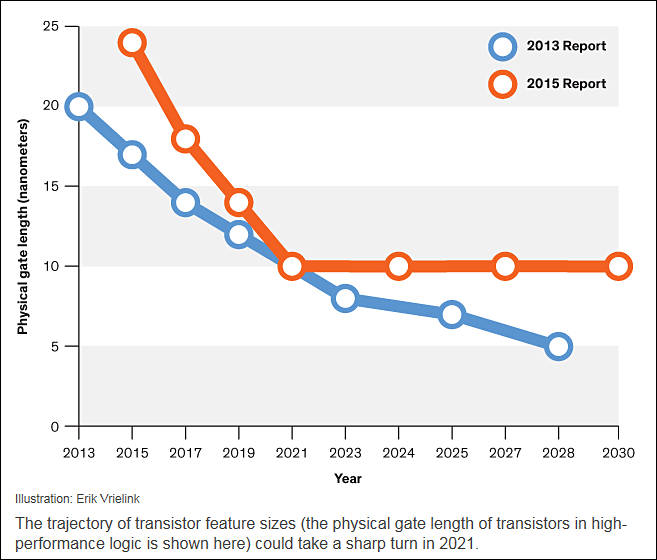

After more than 50 years of miniaturization, the transistor could stop shrinking in just five years, this is the prediction of the 2015 International Technology Roadmap for Semiconductors, which was officially released earlier this month.

After 2021 it will no longer be economically desirable for companies to continue to shrink the dimensions of transistors in microprocessors. Instead, chip manufacturers will turn to other means of boosting density, namely turning the transistor from a horizontal to a vertical geometry and building multiple layers of circuitry, one on top of another.

19 companies were developing and manufacturing logic chips with leading-edge transistors in 2001. Today, there are just four: Intel, TSMC, Samsung, and GlobalFoundries.

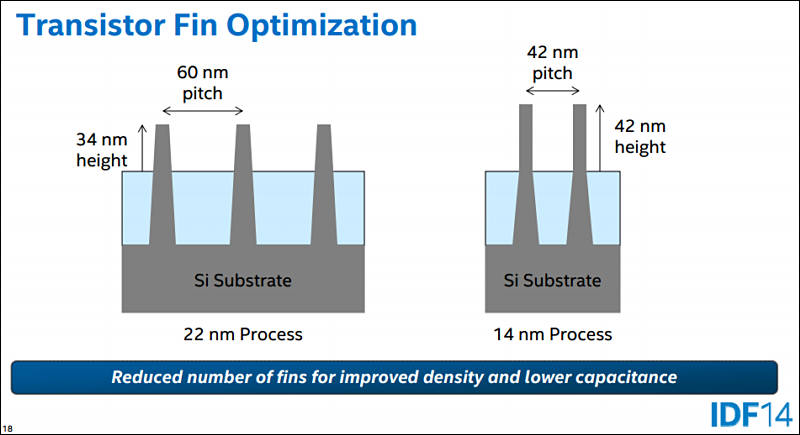

This guys did not tell you full truth. For all last manufacturer processes companies had marketing process values and real process values. In old good times each generation of process really meant proportional reduction of all elements, it is no longer the case. Especially with 14nm processes that are not really 14nm.

Optimistic statements with many 3D wafers and such are overly optimistic. Due to difficulties such process is very costly and available to top manufacturers only. All such processes are not usable in high speed and thermally intense areas due to cooling issues, this mean GPUs and CPUs. Now it is only some flash memory that is made using similar approach.

-

To make thing simple - in early processes all elements scaled proportionally. Already at around 28mm it started to become hard, transistors design changed and only some elements had been scaled while other remained larger. In 14nm it became even worse, 14nm from different manufacturers can differ very much in size. Now 14nm is mostly marketing term.

-

In what regard exactly?

They can no longer scale in frequency so they add cores keeping very big margins.

Most people do not understand that 8x core chip cost to Intel is around 1.5-1.7x compared to more common 4 core chip. So, managers in Intel and press keep people in dark to get big margins and advertisement budgets that come from this same margins.

-

It is not about CPU, it is about Intel 14nm process. I suggest to check specialized resources like EE Times

img975.jpg776 x 299 - 59K

img975.jpg776 x 299 - 59K -

And here is another issue

Sales for the month of June 2016 reached US$26.4 billion, an uptick of 1.1% over the May total of US$26.1 billion, but down 5.8% from the June 2015 total of US$28.0 billion, SIA said. Cumulatively, year-to-date sales during the first half of 2016 were 5.8% lower than they were at the same point in 2015.

With exponentially rising costs of development and manufacturing costs it is not good to have any sales drops.

-

Huge issues with 7nm will follow

The India Lab specifically, in collaboration with MRL-US and Intel product architecture teams worldwide, will spearhead the research and advanced development of Microprocessor Cores in the 2022 and beyond timeframe. By conceiving of and prototyping radical approaches, the Lab will aim to deliver much greater CPU power and area efficiency while still delivering industry-leading performance. The microarchitecture and design of these advanced CPUs will be aggressively co-optimized with Intel's sub-10nm technology nodes deep into the next decade.

It would appear that Intel's new launch time frame for these new processor cores has been pushed out by a couple of years, from 2020 to 2022.

http://www.fool.com/investing/2016/09/02/intel-corporation-may-have-pushed-7-nanometer-tech.aspx

-

Qualcomm Inc. is in talks to acquire NXP Semiconductors NV, a deal that would likely be valued at over $30 billion and represent the latest merger in a rapidly consolidating semiconductor industry.

Huh.

-

Skynet will just have to wait.

-

Who knows..

Google, Facebook, Amazon, IBM and Microsoft are joining forces to create a new AI partnership.

-

Samsing 10nm PR

Following the successful mass production of the industry’s first FinFET mobile application processor (AP) in January, 2015, Samsung extends its leadership in delivering leading-edge process technology to the mass market with the latest offering.

“The industry’s first mass production of 10nm FinFET technology demonstrates our leadership in advanced process technology,” said Jong Shik Yoon, Executive Vice President, Head of Foundry Business at Samsung Electronics. “We will continue our efforts to innovate scaling technologies and provide differentiated total solutions to our customers.”

Samsung’s new 10nm FinFET process (10LPE) adopts an advanced 3D transistor structure with additional enhancements in both process technology and design enablement compared to its 14nm predecessor, allowing up to 30-percent increase in area efficiency with 27-percent higher performance or 40-percent lower power consumption. In order to overcome scaling limitations, cutting edge techniques such as triple-patterning to allow bi-directional routing are also used to retain design and routing flexibility from prior nodes.

The slower the progress - the more PR you need.

-

So it is official now

Qualcomm Incorporated (NASDAQ: QCOM) and NXP Semiconductors N.V. (NASDAQ: NXPI) today announced a definitive agreement, unanimously approved by the boards of directors of both companies, under which Qualcomm will acquire NXP. Pursuant to the agreement, a subsidiary of Qualcomm will commence a tender offer to acquire all of the issued and outstanding common shares of NXP for $110.00 per share in cash, representing a total enterprise value of approximately $47 billion.

https://www.qualcomm.com/news/releases/2016/10/27/qualcomm-acquire-nxp

-

There is evidence that linear scaling has already reached its physical limits. “People say they are doing 10nm process modes, but you will not find any line widths at that level,” Lu says.

That’s why technology development has gone non-linear. In 2011, Intel announced its Tri-gate technology, leading the way from planar development of transistors on silicon into three dimensions. With 3D, even scaling by a factor of 0.85 results in a transistor density that is more like 0.5 scaling in two dimensions, Lu says.

Other companies have followed that trend. Toshiba built 3D NAND in 48 layers, and that memory has been used in Apple’s iPhone 7. Samsung has taken the idea a step further with the creation of a 64-layer flash memory device. The technology level was only 32nm, yet it was the virtual equivalent of 13nm, Lu notes.

“Now we are in silicon age 2.0 with vertical transistors and a scaling parameter of 0.8 to 0.85,” Lu says. “Silicon 3.0 is like a 3D landscape. We are seeing more and more people going there.”

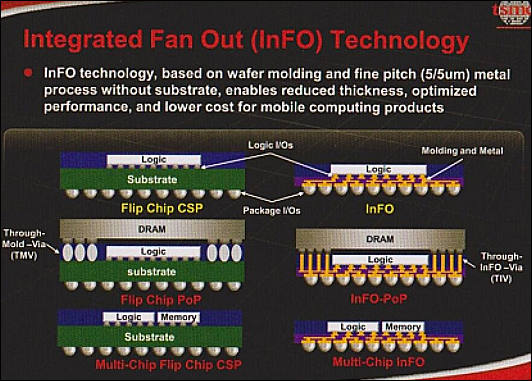

Lu says that his theory, as described in his paper, starts with Silicon 4.0. The advances from the current 3.0 generation have enabled a lot of new applications such as augmented reality, virtual reality and machine intelligence, he says. The next threshold is what Lu calls heterogeneous integration, or the incorporation of silicon and non-silicon materials by means of technologies such as integrated fan out (InFO).

http://www.eetimes.com/document.asp?doc_id=1330750

Note that flip chip shown on the left is widely used in cameras for long.

img2826.jpg532 x 381 - 53K

img2826.jpg532 x 381 - 53K -

Samsung progress

Samsung Electronics is expanding its advanced foundry process technology offerings with the fourth-generation 14-nanometer (nm) process (14LPU) and the third-generation 10nm process (10LPU) to meet the requirements of next generation products ranging from mobile and consumer electronics to data centers and automotives.

Samsung presented these new technology offerings at the Samsung Foundry Forum to foundry customers and partners. The event was held at its Device Solutions America headquarters today, where the company elaborated on the details of new technology offerings including 14LPU and 10LPU.

Samsung’s fourth-generation 14nm process technology, 14LPU, delivers higher performance at the same power and design rules compared to its third-generation 14nm process (14LPC). 14LPU will be optimally suited for high-performance and compute-intensive applications.

-

As the global semiconductor industry moves into the 7nm process, there are only four companies that can offer related products, Globalfoundries, TSMC, Samsung and Intel, of which two are pure-play foundries. We value much the 7nm process believing that this process will be a very important and long-living technology for the semiconductor industry; we have already secured a number of clients and we have great confidence in the 7nm process race.

We decided to jump from 14nm to 7nm directly, while skipping the 10nm process because we believe that 10nm will help not much to improve power consumption and costs for clients; the 10nm node is more like a semi-generation process, similar to the previous the 20nm technology, which could not meet clients' requirements.

-

More details about marketing fluff called "silicon 4.0" mentioned above by eetimes

As for the future of semiconductor technology development, pitch shrinkage technology that has been adopted since the age of Silicon 1.0, is still widely used, but for 10nm, the transistor's shrinkage is actually only 14nm, while 7nm is actually 12nm, and 5nm is only 10nm. So now the semiconductor industry is about to enter the age of Silicon 4.0, said Lu, who added that he refers TSMC's four major growth areas - smartphone, high performance computing (HPC), Internet of Things (IoT) and car-use electronics, which will all be based on its smart semiconductor platform, are the applications targeted in age of Silicon 4.0.

-

Both Taiwan Semiconductor Manufacturing Company's (TSMC) and Samsung's 10nm processes have reached lower-than-expected yield rates, according to industry sources. Yield rates for TSMC's 10nm process technology are not what the foundry expected, the sources said.

Yield rates for Samsung's 10nm process technology have been low prompting Qualcomm to turn cautious about its product roadmap for 2017, the sources said. Qualcomm originally planned for the Snapdragon 835 and other chips including the 660 (codenamed 8976 Plus) built using Samsung's 10nm process, but has revised its roadmap by having only the 835-series made using the newer node technology.

-

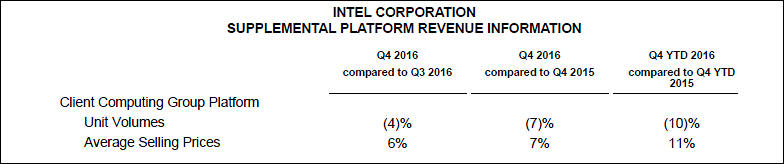

Intel sales dynamics

Number of sold CPU drop, prices rise. All as expected.

sample414.jpg784 x 164 - 30K

sample414.jpg784 x 164 - 30K -

When a manufacturer converts from standard lithography to a double-patterning approach the lithography tool resolution is relaxed, and this shows on the chart’s top blue line. This line shows the lithography requirements for each process. A 45nm process uses 45nm lithography. Since 35nm uses double-patterning, then the lithography backs off to 70nm, and the 25nm process uses 50nm lithography. At 16nm, since quadruple patterning is used, lithography backs off to 4 x 16nm = 64nm.

SDAP limit is around 19nm btw

-

A quick news piece on information coming out of Intel’s annual Investor Day in California. As confirmed to Ashraf Eassa by Intel at the event, Intel’s 8th Generation Core microarchitecture will remain on the 14nm node. This is an interesting development with the recent launch of Intel’s 7th Generation Core products being touted as the ‘optimization’ behind the new ‘Process-Architecture-Optimization’ three-stage cadence that had replaced the old ‘tick-tock’ cadence. With Intel stringing out 14nm (or at least, an improved variant of 14nm as we’ve seen on 7th Gen) for another generation, it makes us wonder where exactly Intel can promise future performance or efficiency gains on the design unless they start implementing microarchitecture changes.

-

I don't understand this slide, supposedly showing the 3-year process advantage Intel has: http://images.anandtech.com/doci/11115/C4PU6KzWMAEglWH_575px.jpg

The 3-year gap they show is comparing Intel's 14nm process to competitors 10nm process. So is Intel saying that their 14nm process achieves higher density than the 10nm process from Samsung and others? And if so, how is this possible?

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,970

- Blog5,724

- General and News1,346

- Hacks and Patches1,153

- ↳ Top Settings33

- ↳ Beginners255

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,360

- ↳ Panasonic990

- ↳ Canon118

- ↳ Sony155

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm100

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras117

- Skill1,961

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips267

- Gear5,414

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,579

- ↳ Follow focus and gears93

- ↳ Sound498

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff272

- ↳ Power solutions83

- ↳ Monitors and viewfinders339

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,319